Rumors Suggest AMD Zen Instruction Set Parity with Haswell/Broadwell

Samuel Wan / 9 years ago

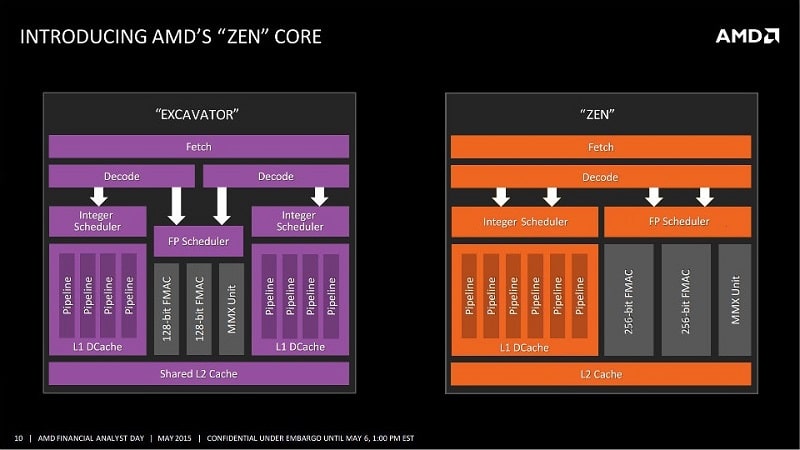

While AMD has released some details about Zen at their Financial Analyst Day earlier this year, details have still been a bit scant. What we already know is that Zen will have a 40% IPC increase compared to Excavator, bringing AMD’s IPC much closer to Intel’s in one jump. Zen will also support a version of Simultaneous Multithreading (SMT) to support 2 logical processors per core. This will all be bundled on the AM4 platform with DDR4 support and use a FinFET process. Most critically, the CMT or cluster-based threading will be gone and each core will have 2 256bit FPUs and a good number of Integer ALUs.

Today though, we have a rumour that suggests that Zen will bring AMD to instruction set parity with Intel’s Haswell/Broadwell CPUs. With Excavator that launched earlier this year, AMD already caught up partially with AVX 2 which brings 256bit support to integer work, BMI2 and RDRAND for pseudo-random number generation. If Zen is to catch up to Haswell, it will probably add hardware acceleration support to CRC, SHA-256 and RSA algorithms and RDSEED for more pseudo-random number generation. interestingly, there is also suggestions that AMD’s SMT implementation will be compatible with the Intel’s meaning OS’s may not need to be patched, like they did with Bulldozer, to fully support the extra logical processor.

AMD may also support some of the new Skylake instructions like AVX 512 though we will have to wait and see. Part of this is due to the fact that Intel is yet to fully reveal what Skylake supports till IDF later this month. With Intel slipping in a refresh with Kaby Lake in 2016, AMD really has a good chance at a comeback if Zen performs well.

Thank you Fudzilla for providing us with the information